Sicherheit für integrierte Schaltungen

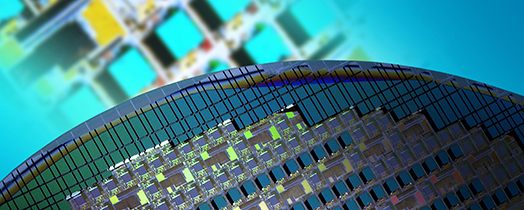

Das Gebiet der Hardware Security konzentriert sich auf Angriffe auf und Schutzmaßnahmen in integrierten Schaltungen, Chips, sowie Baugruppen mehrerer Chips auf Platinen. Die Hauptaufgaben unterteilen sich in die Abwehr von Angreifern, die physischen Zugriff auf ihr Angriffsziel besitzen, und in die Bereitstellung einer grundlegenden Hardware-Sicherheitsebene, auf der weitere Schutzmaßnahmen, zum Beispiel zum Schutz von Betriebssystemen, aufbauen können.

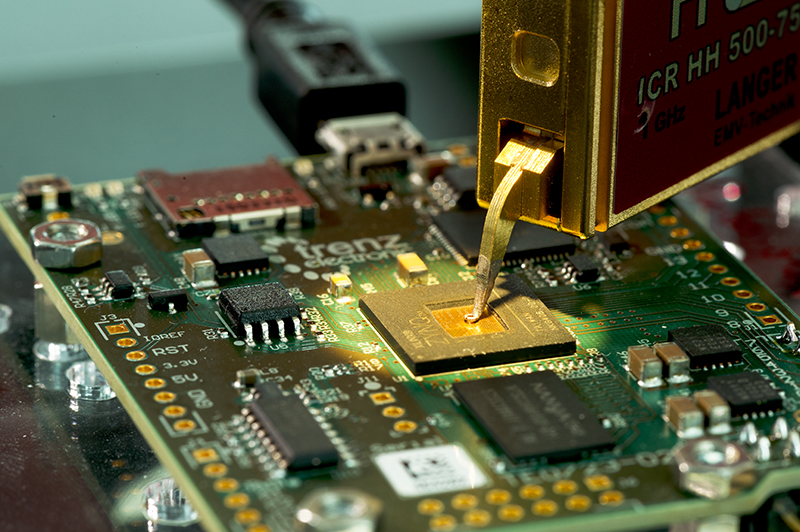

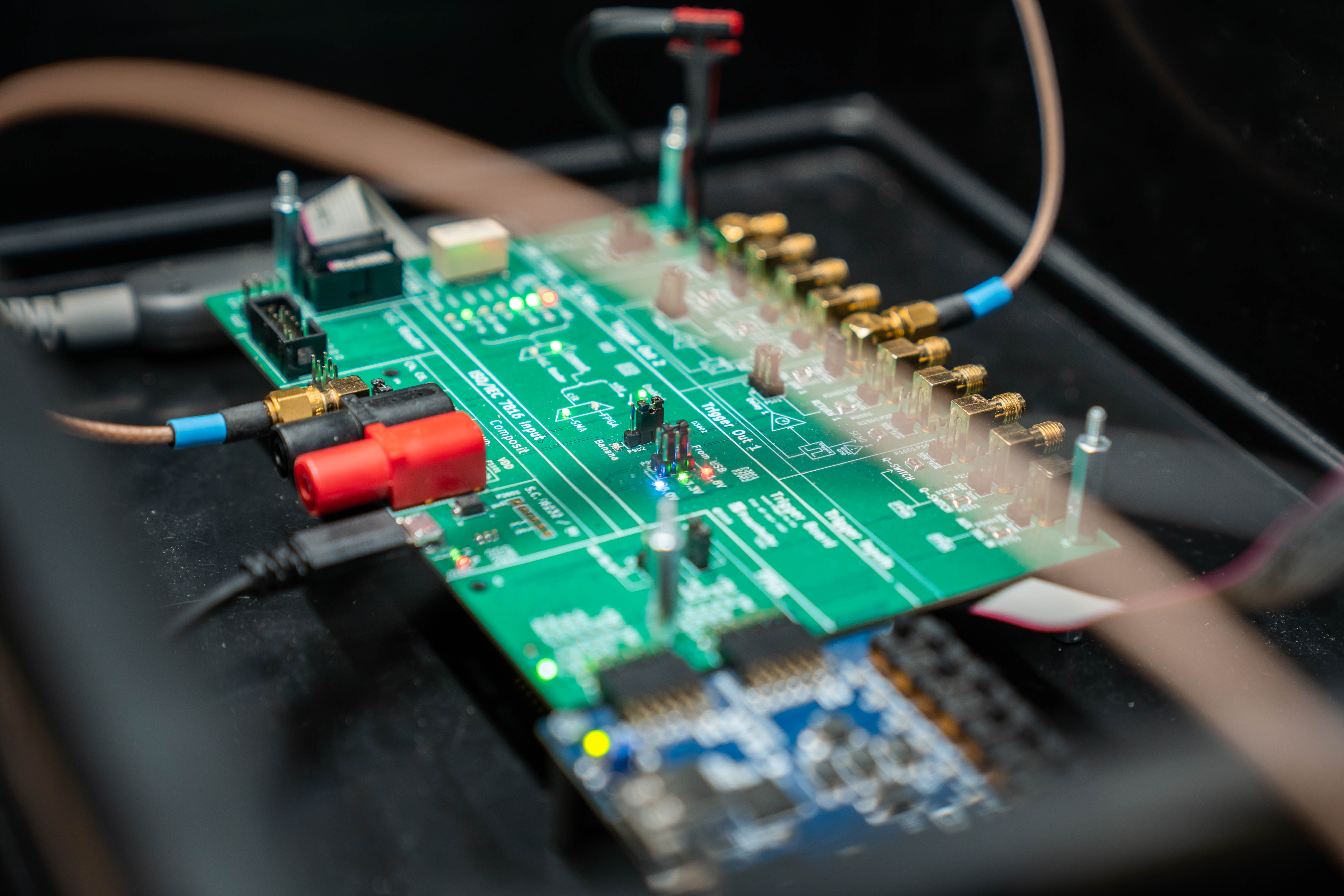

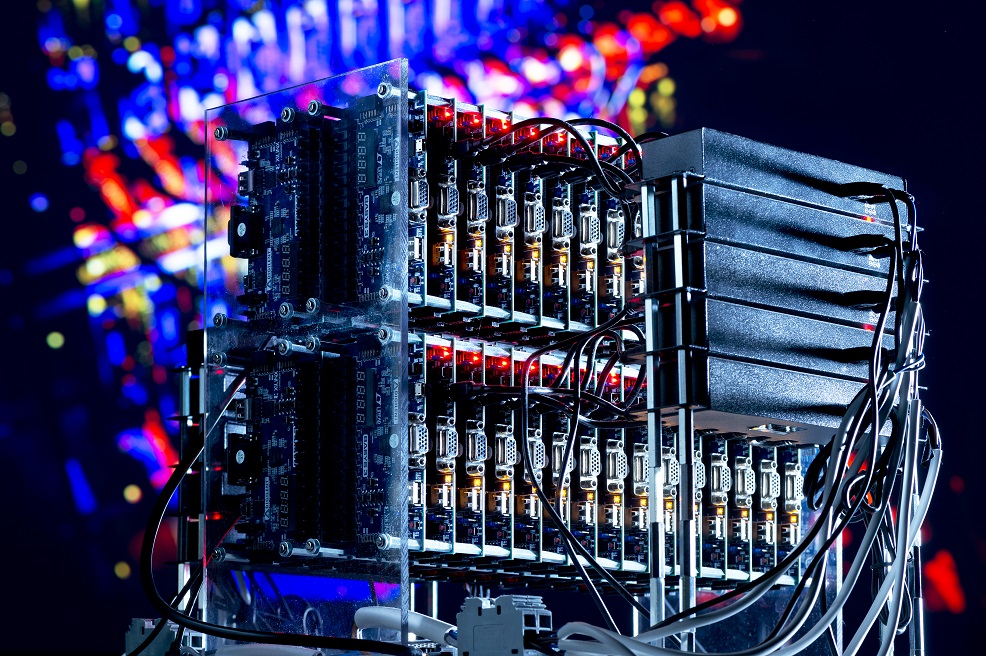

Besondere Schwerpunkte der Forschungsabteilung Hardware Security liegen auf der Sicherheitsevaluierung im Labor, auf der Absicherung und Integration von Mikrocontrollern und Secure Elements sowie auf dem sicheren Einsatz von System-on-Chips und FPGAs. Dabei wird in Bereichen der Seitenkanal-Analyse von kryptographischen Implementierungen, der Fehlerangriffe, des Hardware Penetration Testings, der Physical-Unclonable-Functions (PUF) und des Einsatzes von maschinellen Lernverfahren geforscht und publiziert. Die Ergebnisse erweitern den Stand der Technik in Evaluierung und Schutzmaßnahmen. Dieses ausgeprägte Kompetenzspektrum und die langjährige Erfahrung, sowie die entsprechende Gerätelandschaft mit Tooling im Labor machen es möglich, komplexe Systeme auf Schwachstellen zu untersuchen und individuelle Sicherheitslösungen zu gestalten.

Fraunhofer-Institut für Angewandte und Integrierte Sicherheit

Fraunhofer-Institut für Angewandte und Integrierte Sicherheit